For price, delivery and to place orders: Hittite Microwave Corporation, 20 Alpha Road, Chelmsford, MA 01824

Phone: 978-250-3343 Fax: 978-250-3373 Order On-line at www.hittite.com

Application Support: Phone: 978-250-3343 or apps@hittite.com

FREQUENCY DIVIDERS & DETECTORS - SMT

4

FREQUENCY DIVIDERS & DETECTORS - SMT

4

4 - 1

v01.0414

HMC905LP3E

6 GHz LOW NOISE PROGRAMMABLE

DIVIDER (N = 1 to 4)

General Description

Features

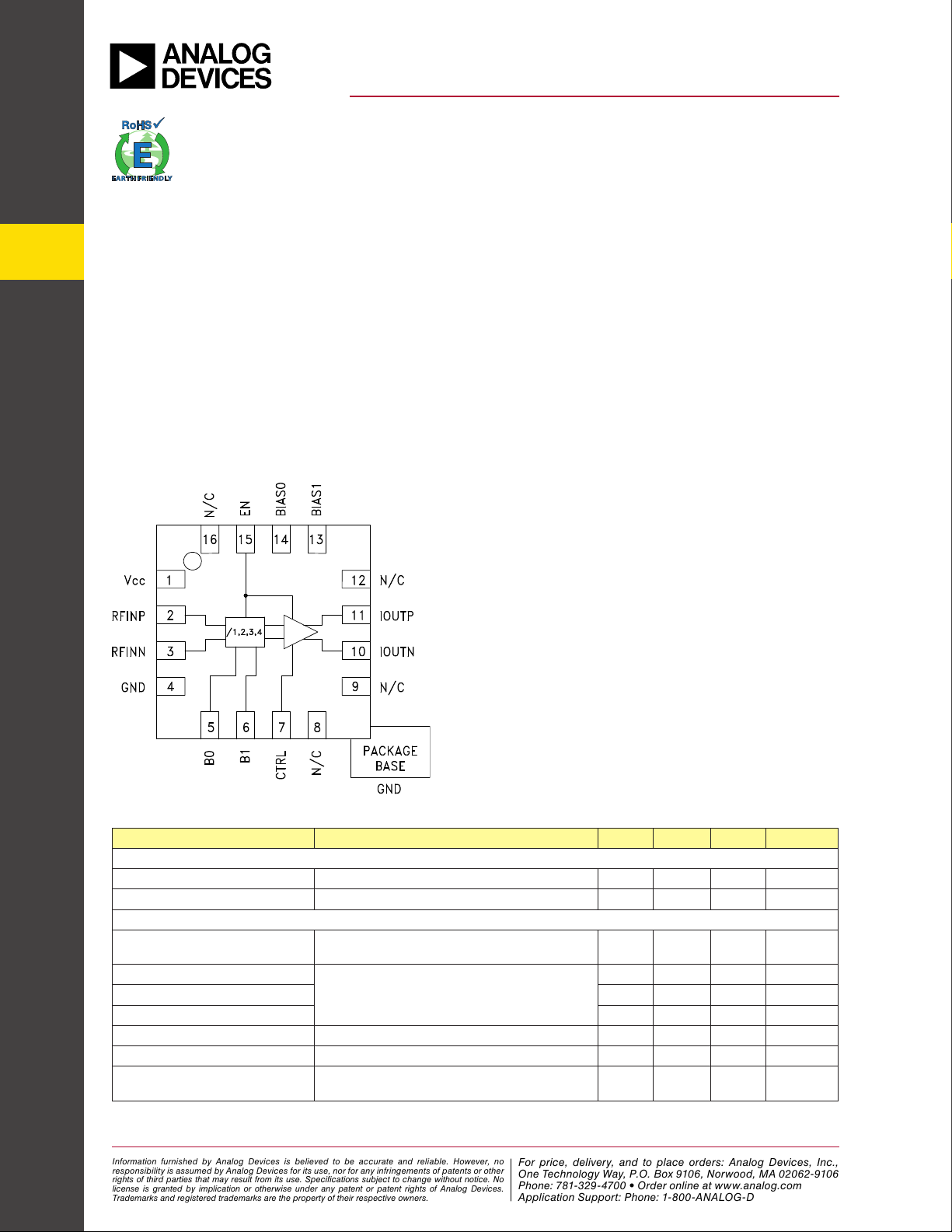

Functional Diagram

Typical Applications

The HMC905LP3E is a SiGe BiCMOS low noise

programmable frequency divider in a 3x3 mm lead-

less surface mount package. The circuit can be pro-

grammed to divide from N = 1 to N = 4 in the 400 MHz

to 6 GHz input frequency range. The high level out-

put power (up to 6 dBm single ended) with a very low

SSB phase noise and 50% duty cycle makes this

device ideal for low noise clock generation, LO

generation and LO drive applications. Congurable

bias and output power controls allow current

consumption and output power control. The device

incorporates a power down feature, good input

to output isolation and fast start up time. The

HMC905LP3E can be included into fast switching

“ping-pong” applications.

Low Noise Floor:

-164 dBc/Hz at 10 MHz Offset for N = 4

Programmable Frequency Divider, N = 1, 2, 3 or 4

400 MHz to 6 GHz Input Frequency Range

Up to +6 dBm Output Power

Sleep Mode: Consumes <1 µA

16 Lead 3X3 mm SMT Package: 9mm

2

Electrical Specications, T

A

= +25° C, Vcc = +3.3V, Z

o

= 50Ω

The HMC905LP3E is ideal for:

• LO Generation with Low Noise Floor

• Software Dened Radios

• Clock Generators

• Fast Switching Synthesizers

• Military Applications

• Test Equipment

• Sensors

Parameter Conditions Min. Typ. Max. Units

RF Input Characteristics

RF Input Frequency Single-ended input 400 6000

[1]

MHz

RF Input Power Single-ended input 0 6 10 dBm

Divider Output Characteristics

Output Power (Single-ended Out)

-Typically, 50 ohms load resistors connected to Vcc

- 1 bit programmable (CTRL digital signal)

[2]

-2 3 6 dBm

SSB Phase Noise @ 10 kHz Offset

+6 dBm Input Power, 6 GHz input,

Single-Ended Input and Output, Divide-by-4

[3]

-150 dBc/Hz

SSB Phase Noise @ 100 kHz Offset -158 dBc/Hz

SSB Phase Noise @ 10 MHz Offset -164 dBc/Hz

Start Up Time EN bit from OFF to ON State (0V to Vcc) 200 ns

Power Down Time EN bit from ON to OFF State (Vcc to 0V) 20 ns

Setting Time at Division Ratio Change

Delay from divide ratio change

to output frequency change

25 ns

[1] Maximum 5500 MHz in Divide by 2.

[2] See typical supply currents vs. BIAS0, BIAS1, CTRL bits table

[3] See Residual Phase Noise plot

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

For price, delivery, and to place orders: Analog Devices, Inc.,

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106

Phone: 781-329-4700 • Order online at www.analog.com

Application Support: Phone: 1-800-ANALOG-D

页面指南