下载

®

Altera Corporation 1

MAX 9000

Programmable Logic

Device Family

June 2003, ver. 6.5 Data Sheet

DS-M9000-6.5

Includes

MAX 9000A

Features...

■ High-performance CMOS EEPROM-based programmable logic

devices (PLDs) built on third-generation Multiple Array MatriX

(MAX

®

) architecture

■ 5.0-V in-system programmability (ISP) through built-in IEEE Std.

1149.1 Joint Test Action Group (JTAG) interface

■ Built-in JTAG boundary-scan test (BST) circuitry compliant with IEEE

Std. 1149.1-1990

■ High-density erasable programmable logic device (EPLD) family

ranging from 6,000 to 12,000 usable gates (see Table 1)

■ 10-ns pin-to-pin logic delays with counter frequencies of up to

144 MHz

■ Fully compliant with the peripheral component interconnect Special

Interest Group’s (PCI SIG) PCI Local Bus Specification, Revision 2.2

■ Dual-output macrocell for independent use of combinatorial and

registered logic

■ FastTrack

®

Interconnect for fast, predictable interconnect delays

■ Input/output registers with clear and clock enable on all I/O pins

■ Programmable output slew-rate control to reduce switching noise

■ MultiVolt

™

I/O interface operation, allowing devices to interface with

3.3-V and 5.0-V devices

■ Configurable expander product-term distribution allowing up to 32

product terms per macrocell

■ Programmable power-saving mode for more than 50% power

reduction in each macrocell

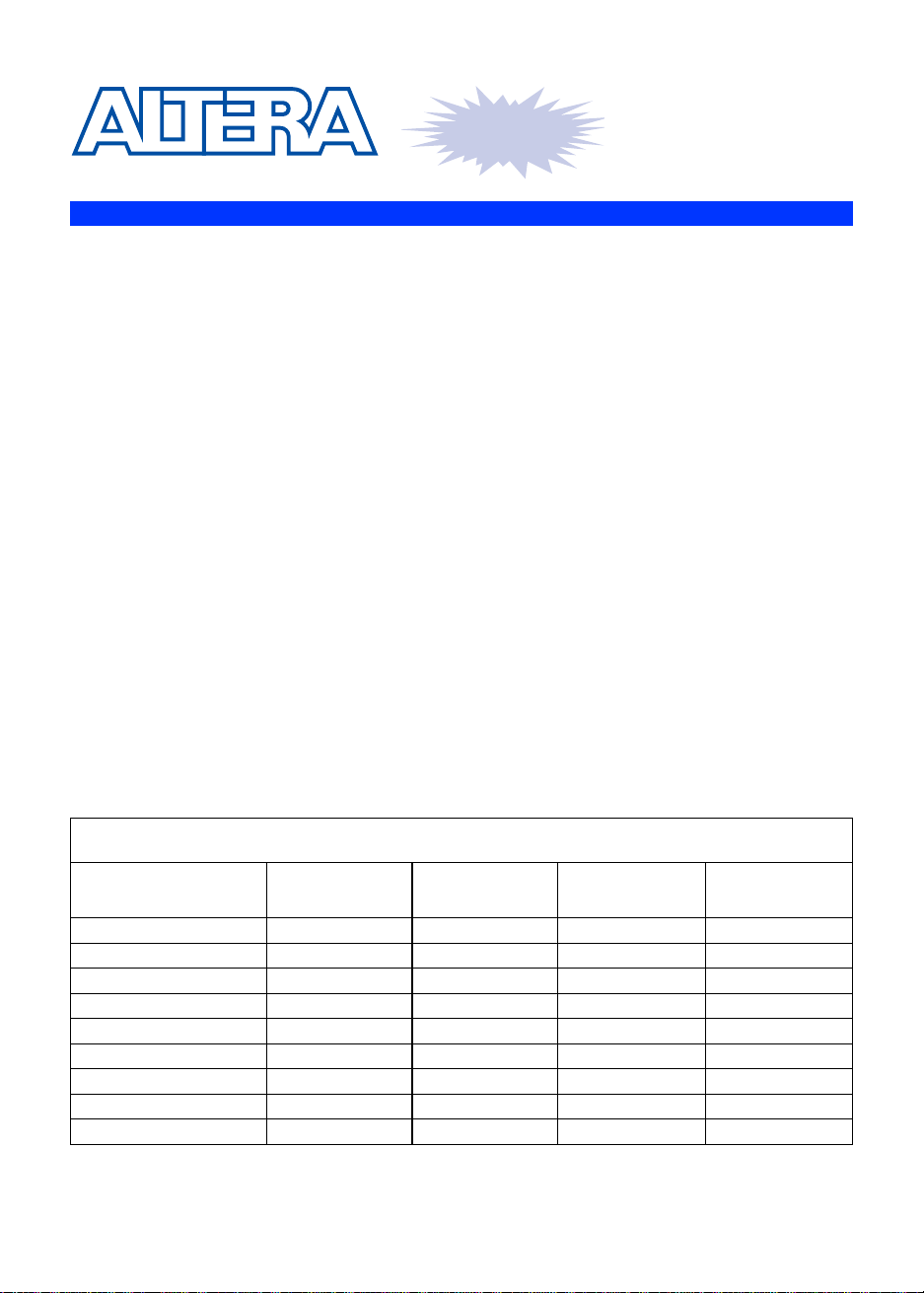

Table 1. MAX 9000 Device Features

Feature EPM9320

EPM9320A

EPM9400 EPM9480 EPM9560

EPM9560A

Usable gates 6,000 8,000 10,000 12,000

Flipflops 484 580 676 772

Macrocells 320 400 480 560

Logic array blocks (LABs) 20 25 30 35

Maximum user I/O pins 168 159 175 216

t

PD1

(ns) 10 15 10 10

t

FSU

(ns) 3.0 5 3.0 3.0

t

FCO

(ns) 4.5 7 4.8 4.8

f

CNT

(MHz) 144 118 144 144