下载

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

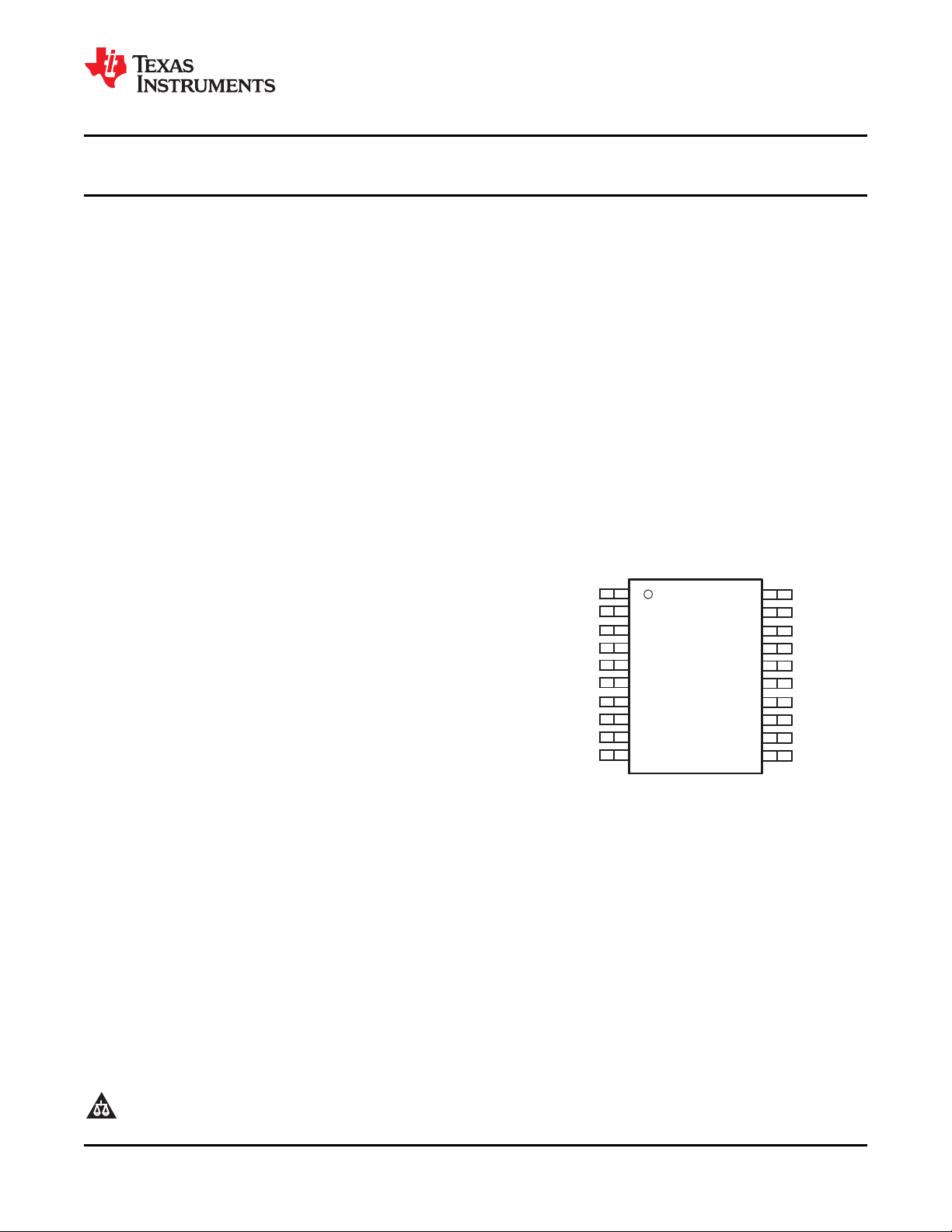

S0/CLK_SEL

S1

V

CC

GND

CLK_IN0

CLK_IN1

GND

SDATA

SCLOCK

Y5

Y4

V

CCOUT2

GND

Y3

Y2

V

CCOUT1

GND

Y1

Y0

TSSOP 20

Pitch0,65mm

6.6x6.6

V

CC

Not Recommended for New Designs

CDC906

www.ti.com

...................................................................................................................................... SCAS828B –SEPTEMBER 2006–REVISED FEBRUARY 2008

PROGRAMMABLE 3-PLL CLOCK SYNTHESIZER / MULTIPLIER / DIVIDER

Check for Samples: CDC906

1

FEATURES

• Commercial Temperature Range 0°C to 70°C

2

• High Performance 3:6 PLL based Clock

• Development and Programming Kit for Easy

Synthesizer / Multiplier / Divider PLL Design and Programming

(TI Pro-Clock™)

• User Programmable PLL Frequencies

• Packaged in 20-Pin TSSOP

• Easy In-Circuit Programming via SMBus Data

Interface • Factory Programmable for Customized Default

Settings are Available. Contact TI Sales Fordes

• Wide PLL Divider Ratio Allows 0-PPM Output

for Further Details.

Clock Error

• Generates Precise Video (27 MHz or 54 MHz)

APPLICATIONS

and Audio System Clocks from Multiple

• Digital TV

Sampling Frequencies (f

S

= 16, 22.05, 24, 32,

• Printer / Scanner

44.1, 48, 96 kHz)

• Set Top Box

• Clock Inputs Accept a Crystal or a

• Video / Audio

Single-Ended LVCMOS or a Differential Input

Signal

TERMINAL ASSIGNMENT

• Accepts Crystal Frequencies from 8 MHz up to

54 MHz

PW PACKAGE

(TOP VIEW)

• Accepts LVCMOS or Differential Input

Frequencies up to 167 MHz

• Two Programmable Control Inputs [S0/S1] for

User Defined Control Signals

• Six LVCMOS Outputs with Output Frequencies

up to 167 MHz

• LVCMOS Outputs can be Programmed for

Complementary Signals

• Free Selectable Output Frequency via

Programmable Output Switching Matrix [6x6]

Including 7-Bit Post-Divider for Each Output

• PLL Loop Filter Components Integrated

• Low Period Jitter (Typical 60 ps)

• Features Spread Spectrum Clocking (SSC) for

Lowering System EMI

• Programmable Center Spread SSC Modulation

(±0.1%, ±0.25%, and ±0.4%) with a Mean Phase

Equal to the Phase of the Non-Modulated

Frequency

• Programmable Down Spread SSC Modulation

(1%, 1.5%, 2%, and 3%)

• Programmable Output Slew-Rate Control

(SRC) for Lowering System EMI

• 3.3-V Device Power Supply

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2Pro-Clock is a trademark of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Copyright © 2006–2008, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.