下载

September 2015 Altera Corporation

ES-01034-1.7 Errata Sheet

Subscribe

© 2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS,

QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries.

All other trademarks and service marks are the property of their respective holders as described at

www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in

accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time

without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or

service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest

version of device specifications before relying on any published information and before placing orders for products or services.

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Errata Sheet for Stratix V Devices

This errata sheet provides information about known device issues affecting Stratix

®

V

production devices.

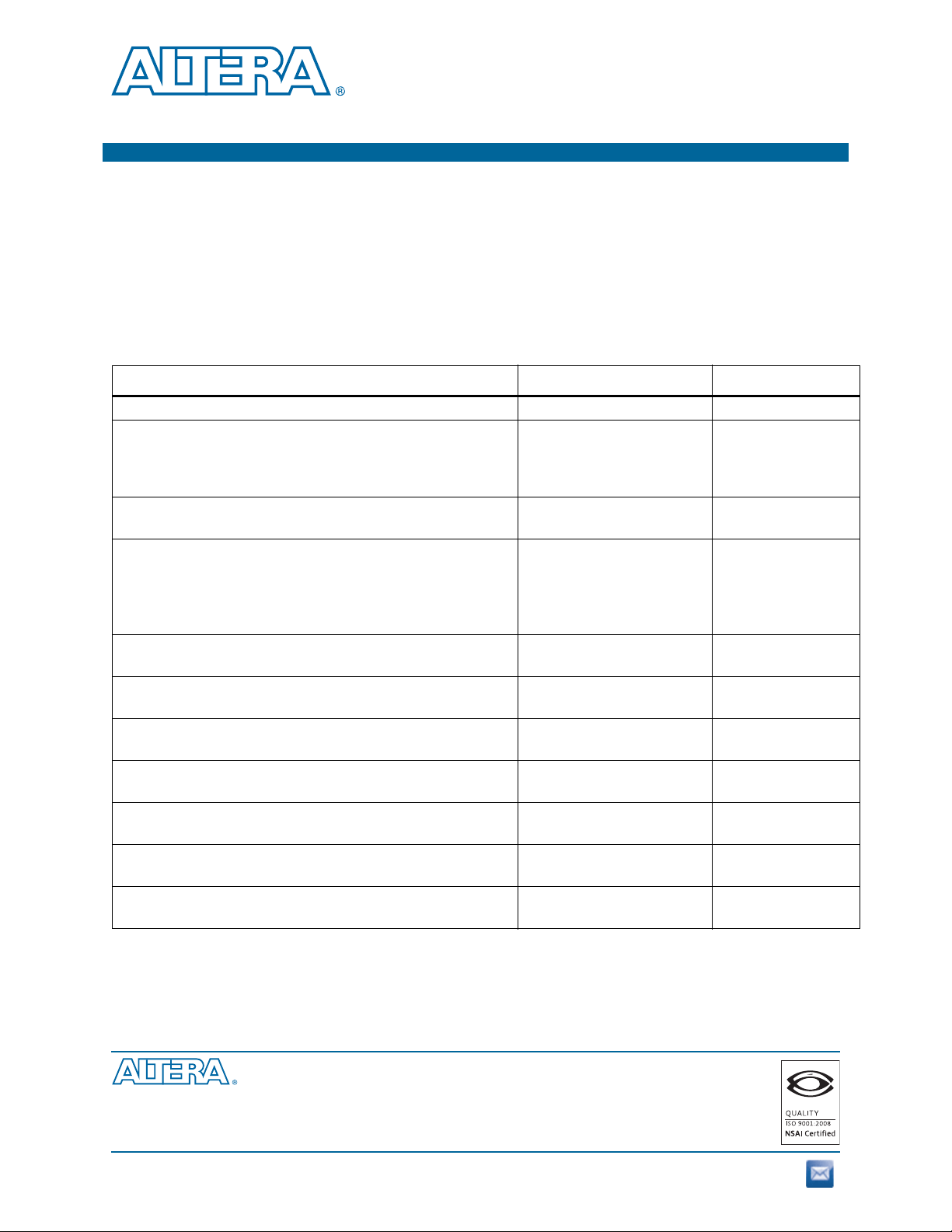

Production Device Issues for Stratix V Devices

Table 1 lists the issues and the affected Stratix V production devices.

Table 1. Stratix V Production Device Issues (Part 1 of 2)

Issue Affected Devices Planned Fix

“JTAG Programming of 28-nm Devices” All Stratix V production devices None

“PCIe Gen2 Link Training Error When Using Hard Reset Controller” All Stratix V production devices

Software will default to

Soft Reset Controller in

Quartus II version

13.1.

“LVDS Soft-CDR and DPA Modes”

All Stratix V GX/GS/GT

production devices

None

“Receiver Detect Issue in the PCIe Hard IP”

5SGXA7, 5SGXA5, 5SGXA4,

5SGXA3, 5SGSD5, 5SGSD4,

5SGSD3, 5SGTC7, 5SGTC5

5SGXB5, 5SGXB6,

5SGSD6, 5SGSD8,

5SGXA9, 5SGXAB,

5SGXB9, 5SGXBB,

5SEE9, 5SEEB

“Partial Reconfiguration (PR) with Compression Not Supported in

Configuration via Procotol (CvP) when Encryption Disabled”

All Stratix V production devices None

“False Configuration Failure in Active Serial Multi-Device

Configuration x1 Mode”

All Stratix V production devices None

“CMU PLL Range”

All Stratix V GX and GS

production devices

None

“Production Device Supply Voltage Requirements”

All Stratix V GX and GS

production devices

None

“ATX PLL Range”

All Stratix V GX/GS/GT

production devices

For faster operation,

contact mySupport.

“Unused or Idle Clock Performance Degradation”

All Stratix V GX/GS/GT

production devices

None

“RREF Calibration Resistor Value Changed from 2k to 1.8k”

All Stratix V GX/GS/GT

production devices

None