下载

© Semiconductor Components Industries, LLC, 2014

November, 2014 − Rev. 9

1 Publication Order Number:

NB6L11S/D

NB6L11S

2.5 V 1:2 AnyLevel] Input

to LVDS Fanout Buffer /

Translator

The NB6L11S is a differential 1:2 clock or data receiver and will

accept AnyLevel™ input signals: LVPECL, CML, LVCMOS, LVTTL,

or LVDS. These signals will be translated to LVDS and two identical

copies of Clock or Data will be distributed, operating up to 2.0 GHz or

2.5 Gb/s, respectively. As such, the NB6L11S is ideal for SONET,

GigE, Fiber Channel, Backplane and other Clock or Data distribution

applications.

The NB6L11S has a wide input common mode range from

GND + 50 mV to V

CC

− 50 mV. Combined with the 50 W internal

termination resistors at the inputs, the NB6L11S is ideal for translating

a variety of differential or single−ended Clock or Data signals to

350 mV typical LVDS output levels.

The NB6L11S is the 2.5 V version of the NB6N11S and is offered in

a small 3 mm X 3 mm 16−QFN package. Application notes, models,

and support documentation are available at www.onsemi.com

.

Features

• Input Clock Frequency > 2.0 GHz

• Input Data Rate > 2.5 Gb/s

• RMS Clock Jitter −0.5 ps, Typical

• 622 Mb/s Data Dependent Jitter − 6 ps, Typical

• 380 ps Typical Propagation Delay

• 120 ps Typical Rise and Fall Times

• Single Power Supply; V

CC

= 2.5 V " 5%

• These are Pb−Free Devices

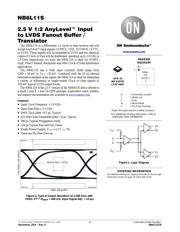

TIME (58 ps/div)

Figure 2. Typical Output Waveform at 2.488 Gb/s with

PRBS 2

23−1

(V

INPP

= 400 mV; Input Signal DDJ = 14 ps)

VOLTAGE (130 mV/div)

Device DDJ = 10 ps

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

G = Pb−Free Package

*For additional marking information, refer to

Application Note AND8002/D.

MARKING

DIAGRAM*

QFN−16

MN SUFFIX

CASE 485G

www.onsemi.com

See detailed ordering and shipping information in the package

dimensions section on page 10 of this data sheet.

ORDERING INFORMATION

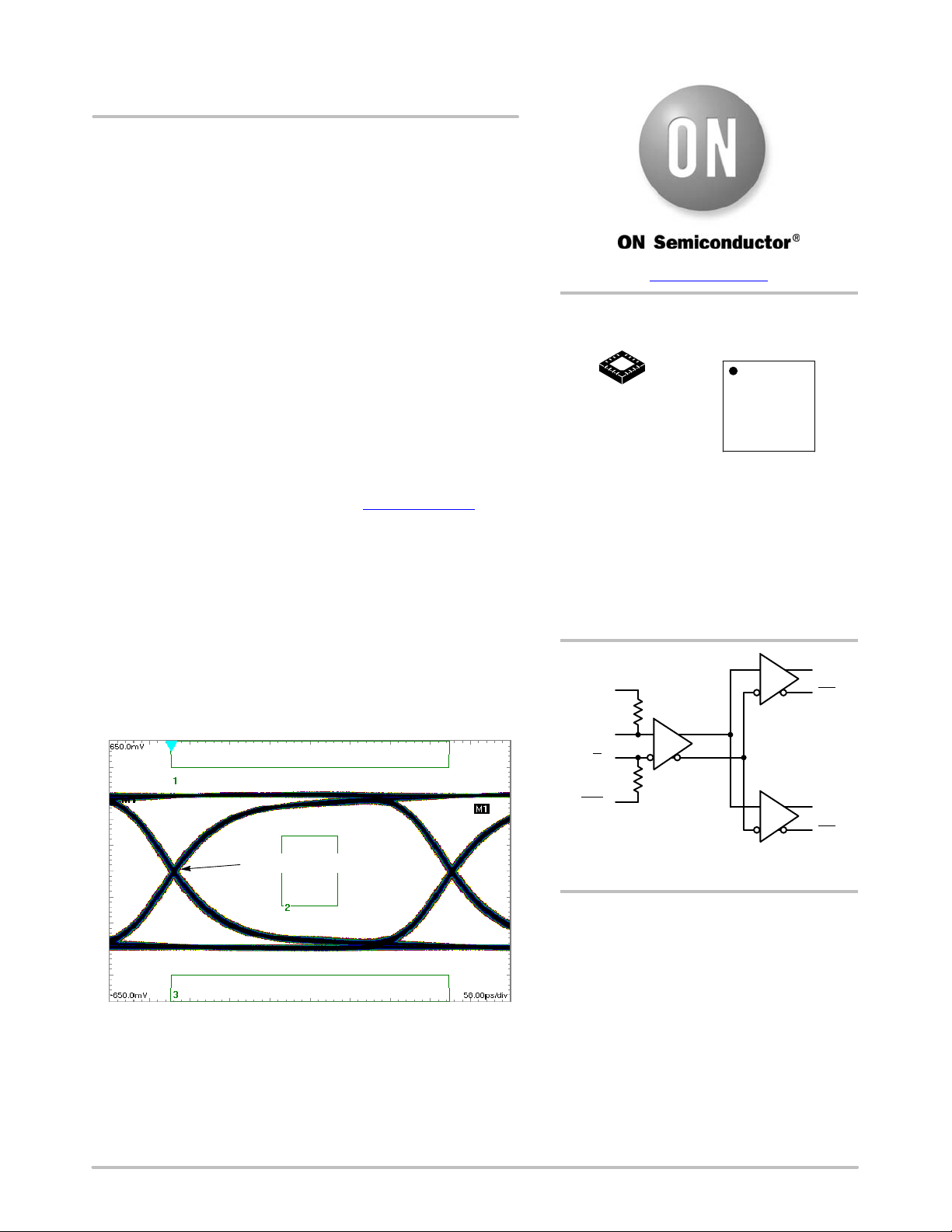

16

NB6L

11S

ALYW G

G

1

1

Q0

Q0

Q1

Q1

D

D

V

TD

V

TD

Figure 1. Logic Diagram

(Note: Microdot may be in either location)

页面指南